ЛЖгфЏРРЩюлкЪаЕТСЂЁюЪЂПЦММгаЯоЙЋЫОЙйЭј

0755-28286748

ДњРэЩЬ

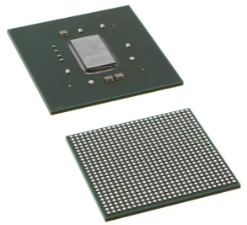

The Zynq? UltraScale+? MPSoC family is based on the Xilinx? UltraScale? MPSoC architecture. This family of products integrates a feature-rich 64-bit quad-core or dual-core Arm? Cortex?-A53 and dual-core Arm Cortex-R5 based processing system (PS) and Xilinx programmable logic (PL) UltraScale architecture in a single device. Also included are on-chip memory, multiport external memory interfaces, and a rich set of peripheral connectivity interfaces. Processing System (PS) Arm Cortex-A53 Based Application Processing Unit (APU) ? Quad-core or dual-core ? CPU frequency: Up to 1.5GHz ? Extendable cache coherency ? Armv8-A Architecture o 64-bit or 32-bit operating modes o TrustZone security o A64 instruction set in 64-bit mode, A32/T32 instruction set in 32-bit mode ? NEON Advanced SIMD media-processing engine ? Single/double precision Floating Point Unit (FPU) ? CoreSight? and Embedded Trace Macrocell (ETM) ? Accelerator Coherency Port (ACP) ? AXI Coherency Extension (ACE) ? Power island gating for each processor core ? Timer and Interrupts o Arm Generic timers support o Two system level triple-timer counters o One watchdog timer o One global system timer ? Caches o 32KB Level 1, 2-way set-associative instruction cache with parity (independent for each CPU) o 32KB Level 1, 4-way set-associative data cache with ECC (independent for each CPU) o 1MB 16-way set-associative Level 2 cache with ECC (shared between the CPUs) Dual-core Arm Cortex-R5 Based Real-Time Processing Unit (RPU) ? CPU frequency: Up to 600MHz ? Armv7-R Architecture o A32/T32 instruction set ? Single/double precision Floating Point Unit (FPU) ? CoreSight? and Embedded Trace Macrocell (ETM) ? Lock-step or independent operation ? Timer and Interrupts: o One watchdog timer o Two triple-timer counters ? Caches and Tightly Coupled Memories (TCMs) o 32KB Level 1, 4-way set-associative instruction and data cache with ECC (independent for each CPU) o 128KB TCM with ECC (independent for each CPU) that can be combined to become 256KB in lockstep mode On-Chip Memory ? 256KB on-chip RAM (OCM) in PS with ECC ? Up to 36Mb on-chip RAM (UltraRAM) with ECC in PL ? Up to 35Mb on-chip RAM (block RAM) with ECC in PL ? Up to 11Mb on-chip RAM (distributed RAM

? Consumer Electronics ? Compute and Storage ? Wireless Communications ? Industrial Control Systems ? Automotive System

| аЭКХ | DataSheet | Dimension (mm) | Description |

|---|